**BEST: International Journal of Management, Information**

Technology and Engineering (BEST: IJMITE)

ISSN 2348-0513

Vol. 2, Issue 1, Jan 2014, 83-90

© BEST Journals

A NEURAL APPROACH TO PERFORM NOISE REDUCTION OVER FIR FILTER

AVNESH VERMA<sup>1</sup>, SURINDER SINGH<sup>2</sup> & RAHMI SAINI<sup>3</sup>

<sup>1,2</sup>Assistant Professor, Department of Instrumentation, Kurukshetra University, Haryana, India

<sup>3</sup>Research Scholar, Dissertation Scholar, Department of Instrumentation, Kurukshetra University, Haryana, India

ABSTRACT

A signal to be digitized is passed through an analog anti-aliasing filter just prior to the Analog to Digital

Converter to remove those components that the digitizing process would mirror to the needed frequency band (aliases).

At high sampling rates, and the associated frequencies, we require some anti-aliasing filter that should be simple and

inexpensive. The presented work is about the optimization of FIR filter using neural network. The work is implemented to

remove the non linearity over the optical signal. The obtained results shows the effectiveness of the work, in terms of more

linear the signal is, with the reduction of error over the signal.

KEYWORDS: FIR, Filter, Neural Network, Noise

INTRODUCTION

In digital signal processing, analog signals are converted to digital samples at some stage of the signal processing.

Such kind of signals also contains the problem of noise, distortion components, unwelcome external signals, cross-talk, etc.

These all impurities over the signal disrupt the signal and affect the overall throughput. To get the effective outcome it is

required to remove all such impurities over the signal. It is required to design such a digital signal that will provide more filtered and the accurate output. The main objective of the filter design is to achieve more accurate and error free signal

processing so that they do not depend on component tolerances, etc. After digitizing a complex sine wave of a specific

frequency domain f, it is not required to differentiate between the infinitely many sine waves at frequencies  $f \pm k \cdot f_{Samp}$

(k integer). If the signal is real, the frequencies  $-f \pm k \cdot f_{Samp}$  are also seen.

A foreign signal can be at a distant frequency and still one of its aliases interferes with the useful signal.

There is no such signal that can resolve all the impurities. Therefore an analog filter has to be applied to the signal prior to

the analog to digital conversion to limit the bandwidth so most interfering signals that could alias to the useful frequency is

filtered from the impurities such kind of filtration is represented by anti-aliasing filter. Such kind of filters are mainly

beneficial when the signal frequency is high and the more distortion present over the signal. These filters provide the

effective and error free signal at low error rate and with high throughput.

Before this digitizing some signals need to be mixed into a fixed Intermediate Frequency (IF) band.

As the frequency of the frequency band increases, there are the higher chances of the signal interferences. As the distance

of these interferences from the actual signal is increases, it is easy to implement the filter and to obtain the needed signal

from the signal defined in actual. Therefore it is advantageous to choose a high frequency signals. Such kind of signals also

requires the high sample rate so that the attenuation over the signal will be minimum, it will give the easy measures to the

signal and will reduce the overall error rate for the signal

These show that it has every advantage of having high sampling rates, besides its cost, which is customarily

meagre than the cost of a commensurable analog solution. Here the sample rate also defines the size of the dataset.

It means higher the sample rate, larger the dataset will be. The large dataset again represents the higher requirement of the power and the memory. Such kind of filters requires some extra hardware implementation that can also solve these problems with low cost but software decimation on general purpose DSPs is more flexible and easier to develop than hardware. Improvements in FIR equalization using FFTs or partial FFTs leads mathematically closer to OFDM. Lot of work is done by many researchers to perform the FIR equivalization by using different approaches. Some of such work is defined here with.

## **Earlier Work**

In year 2007, Nilanjan Banerjee performed a work on the process variation aware methodology to work on Fixedpoint FIR filters. The author has defined a novel FIR filter synthesis technique that allows aggressive voltage scaling by exploiting the fact that all filter coefficients are not equally important to obtain a "reasonably accurate" filter response[1]. In year 2002, Jongsun Park performed a work on "High Performance and Low Power FIR Filter Design Based on Sharing Multiplication". The author described about the high performance and low power FIR filter design, which genuinely represents the computation sharing multiplier (CSHM).

CSHM concretely targets computation re-use in vector-scalar products and is efficaciously utilized in Presented FIR filter design [2]. In year 2011, Angelo G. da Luz performed the exploration of different heuristic-based algorithms for the best factorization of the signal under the concept of Finite Impulse Response (FIR) filters. A new heuristic-based algorithm named Anedma is proposed to get as near as possible to the optimal solution for the ordering and partitioning of larger filter instances [3].

In year 2004, Vagner S. Rosa defined an effective work pm the hardwired FIR filter. The work is about to design parallel digital finite impulse response (FIR) filters for hardwired (fixed coefficients) implementation with reduced number of adders and logic depth in the multiplier block [4]. In year 2010, Angelo G. da Luz performed a work, "Ordering and Partitioning of Coefficients Based on Heuristic Algorithms for Low Power FIR Filter Realization". An ameliorated finite FIR filter is defined in an efficacious way so that the actual representation and the factorization of the coefficients can be represented in an optimized form. For this work, a improved complete optimization process is implemented again using the hybrid approach [5].

In year 2001, Mitsuru Yamada performed a work, "High-Speed FIR Digital Filter with CSD Coefficients Implemented on FPGA". Based on this hardware based architecture an efficient and the low complexity FIR filter is designed. The another kind of digital filter is the Multipliers that defined the coefficients as canonic signed digit (CSD) code are realized with wired-shifters, adders and substracters.

The critical path is minimized by insertion of pipeline registers and is equal to the propagation and also represents the propagation delay. It also defines the pipelined registers as it is limited by using an equivalent transformation on a signal flow graph[6]. In year 2007, Levent Aksoy performed a work based on gray level metrics to optimize the Digital FIR filter.

The author has defined an analytical metrics for the minimization of area in the generic problem of multiple constant multiplications; it also increased the efficiency and the effectiveness of the FIR filter design. Author make the observation that not all of these operations without affecting the cost of the hardware design. The algorithm defined by the author is the minimum cost solution that provides the considering area estimates for each operation. To this end[7].

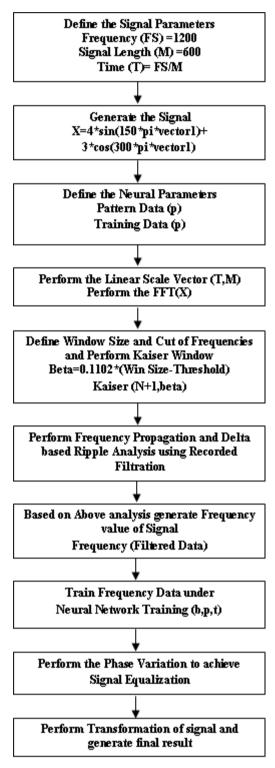

Figure 1: Proposed Methodology

In year 2000, Vijay Sundararajan performed a work "Synthesis of low power folded programmable coefficient FIR digital filters". The author has discussed and designed a potency efficacious synthesis technique to design the folded or time-multiplexed FIR filters where storage area is traded-off for lowering power consumption. A systematic technique is developed for low power mapping of FIR filters to architectures with arbitrary number of minute digital signals are included in the work. These digital components are combined in such a way so that the overall power consumption is reduced by reducing switching activity at both the data-input as well as the coefficient input. Common input operands can be exposed by unfolding, which, however leads to a memory increase[8].

## FILTER DESIGN

A half band filter (a FIR filter of cut off frequency = ½, if the pass-band and stop band are mirror images) can have almost every second coefficient 0 (non-zero in the middle of odd coefficient sequences). It allows improving the processing speed of the work to the doubled value. The work has presented the results using the multi-rate decimator that gives the advantage of highly efficient processing over the signal. Whereas the disadvantage associated with the work is the length and complexity of the code.

### m'th Band Filter

The direct decimation by d filters can have every d'th coefficient as 0 – except the middle one when they form m'th band filters (with special symmetry in the frequency response curve). The effectiveness of the work yield to the optimum outcome along with the efficient processing achieved from the filter. The presented system is based on the trivial modification so that lesser improvement are required to optimize the signal. The filter basically modifies the matrix and deletes the columns from the matrices, which correspond to the 0 coefficients.

### Other 0 Coefficients

We can force any other coefficients to 0, it will first identify the 0 valued columns from the matrix and then delete all such columns. The elimination of such columns overall affect the quality of the signal. The another way is to eliminate the tail coefficients with 0 values so that the length of the signal will be reduced and effective communication of the signal will be gained.

# **COMB FILTER STAGES**

The first few stages of a multi-rate decimation process could use comb filters i.e. FIR filters with equal coefficients. These kind of filters and designed as an IIR filter so that some addition to the filter loop will be performed On the down side, all the output samples have to be generated now, and thrown away except every *d*-th one. Only if multiplications are very expensive compared to integrations, the advantages of a few comb filter decimation stages can outweigh the savings due to not calculating the discarded samples, what is possible with a true FIR decimation filter.

The presented work is based on the coefficient oriented FIR filter with FFT based filtration and the neural network based optimization. Such kind of work is very similar to the definition of OFDM signals. In this work we have initially defined the signal under some parameters like signal length, frequency etc. Once the signal defined, the initial filtration is performed using FFT, window size adjustment and the cut off frequency. After this, the second level of filtration is been performed by using Kaiser filtration. It will reduce major impurities over the signal, but to perform a low level of equalization frequency propagation and the ripple frequency analysis is been performed on this work. Based on this all the statistical analysis based reduction of noise will be performed. Now to achieve more refined signal, the obtained frequency value is trained under the neural network with some pattern definition and the training dataset. It will perform the train the parameters under defined coefficient and constraints and optimize the signal to achieve the noise reduction over the signal. The parametric algorithm of proposed work is defined in figure 1. In this work we have presented a neural network based optimized FIR filter. The process flow of the given work is shown in figure 1.

## **NEURAL NETWORKS**

The term neural network was traditionally used to refer to a network or circuit biological neurons. Today these neural networks are presented in a simulated environment where it is called Artificial Neural network. This concept is

defined with the nodes under the intelligent process implemented by the neural network. A neural network basically work on some training data that represents the previous output so that the current input and the previous output collectively analyzed and generate a new outcome from the dataset. Based on this analysis, a structural back-propagation approach is defined by the neural phenomenon.

### **Back Propagation Neural Network**

Back propagation is a common method of teaching artificial neural networks how to process on any give data set under the defined methodology. Such kind of concept is actually presented by Arthur E. Bryson and Yu-Chi Ho in 1969, but it wasn't until 1974 and later on it was been processed by Paul Werbos. David E. Rumelhart, Geoffrey E. Hinton and Ronald J. Williams, that gained recognition, and it led to a "renaissance" in the field of artificial neural network research.

It is a supervised and the semi supervised learning approach that basically represents the delta rule of classification. Such supervised approach actually need some controller that will setup the constraints to the system, estimate the effectiveness of the system and the observe and analyze the outcomes from the system. Such a supervised approach is beneficial in Feed forward neural network as there is no looping for the feedback. In case of back propagation method the feedback from the system is additionally driven to obtain the next level results.

# **Propagation**

Each Propagation Involves the Following Steps

- Forward propagation of a training pattern's input through the neural network in order to engender the propagation's output activations.

- Back propagation of the propagation's output activations through the neural network utilizing the training pattern's target in order to engender the deltas of all output and obnubilated neurons.

# Weight Update

For each weight-synapse

- Multiply its output delta and input activation to acquire the gradient of the weight.

- Bring the weight in the antithesis direction of the gradient by subtracting a ratio of it from the weight.

This ratio influences the speed and quality of learning; it is called the cognition rate. The designation of the gradient of a weight designates where the error is incrementing; this is why the weight must be updated in the antithesis direction.

# **ALGORITHM**

Step 1: Initialize the input and assign weights to them accordingly

**Step 2:** Train the input for N datasets

**Step 3:** For Each Training Set I in N [Repeat Steps 4 to ]

**Step 4:** Set O= Neutral Output (Network, I)

**Step 5:** Set T= Throughput of I

Step 6: Calculate Error T-O

- Step 7: Compute W1=All Weights from Hidden Layer to Output Layer

- Step 8: Compute W2=All Weights from Input Layer to Hidden Layer

- **Step 9:** Update Weights in the Network

- **Step 10:** Go to Step 3 Until Classification not done correctly.

# RESULTS AND DISCUSSIONS

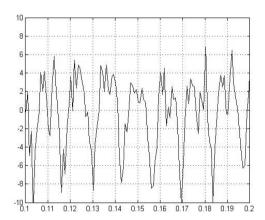

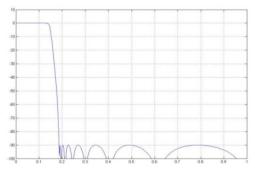

The presented work is implemented in MatLab 7.10. Here figure 3 is showing the effect of filtration process over the optical filter. The figure is showing that the FIR filter has removed most of the noise and non linearity over the signal and provide the smoothness in signal. Here figure 2 is showing the input signal. Here x axis represents the length y axis represents the amplitude variation over the signal.

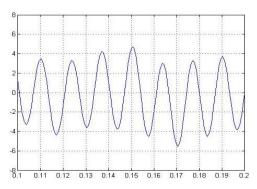

As we can see the figure 3 is showing the non-linearity or the error reduced from the signal and figure 4 is showing the final results.

Figure 2: Randomly Generated Signal

Figure 3: Non Linearity Reduced

Figure 4: Final Result

# **CONCLUSIONS**

The presented work is about the construction of FIR filter so that the impurities over the signal can be reduced. In this work we have defined a neural network inspired approach to remove the impurities over the signal. The results obtained shows that the present work has removed most of the impurities from the signal. The final signal received after processing is the improved signal and more refined signal from the work.

# REFERENCES

- 1. Nilanjan Banerjee, Jung Hwan Choi and Kaushik Roy (2007). A process variation aware low power synthesis methodology for fixed-point FIR filters. ISLPED'07 Proceeding of the 2007 International Symposium on Low Power Electronics and Design, 147-152.

- Jongsun Park, Woopyo Jeong, Hunsoo Choo, Hamid Mahmoodi-Meimand, Yongtao Wang and Kaushik Roy (2002). High performance and low power FIR filter design based on sharing multiplication. ISLPED'02 Proceeding of the 2002 International Symposium on Low Power Electronics and Design, 295-300.

- Angelo G. da Luz, Eduardo A. C. da Costa and Marilton S. de Aguiar (2011) Exploring the use of heuristic-based algorithms for the ordering and partitioning of coefficients for power efficient fir filters realization SBCCI '11 Proceedings of the 24th symposium on Integrated circuits and systems design, 91-96.

- Vagner S. Rosa, Eduardo Costa, José C. Monteiro and Sergio Bampi (2004). An Improved Synthesis Method for Low Power Hardwired FIR Filters. SBCCI'04, Proceedings of the 23<sup>rd</sup> symposium on Integrated circuits and systems design, Pernambuco, Brazil.

- Angelo G. da Luz, Eduardo A.C da Costa and Marilton S. de Aguiar (2010). Ordering and partitioning of coefficients based on heuristic algorithms for low power FIR filter realization SBCCI '10 Proceedings of the 23rd symposium on Integrated circuits and system design, 180-185.

- Mitsuru Yamada and Akinori Nishihara (2001). High-Speed FIR Digital Filter with CSD Coefficients

Implemented on FPGA, ASP-DAC '01 Proceedings of the 2001 Asia and South Pacific Design Automation

Conference, 7-8.

- 7. Levent Aksoy, Eduardo A. C. da Costa, Paulo F. Flores and José C. Monteiro (2007). Optimization of Area in Digital FIR Filters using Gate-Level Metrics, Proceedings of the IEEE Workshop on Signal Processing Systems, SiPS 2007, 420-423.

- Vijay Sundararajan and Keshab K. Parhi (2000). Synthesis of low power folded programmable coefficient FIR digital filters, ASP-DAC '00 Proceedings of the 2000 Asia and South Pacific Design Automation Conference, 153-156